8255:

The INTEL 8255 is a device used to implement parallel data transfer between the processor and slow peripheral devices like ADC, DAC, keyboard, 7-segment display, LCD, etc. The 8255 has three ports:

- Port-A

- Port-B

- Port-C

Ports A and B are 8-bit parallel ports. Port-A can be programmed to work in any one of the three operating modes as an input or output port. The three operating modes are:

-

Mode-0 → Simple IO port

Mode-1 → Handshake IO port

Mode-2 → Bidirectional IO port

Port-B can be programmed to work either in mode-0 or mode-1 as an input or output port. Port-C pins (8 pins) have different assignments depending on the mode of ports A and B. If ports A and B are programmed in mode-0, then port C can perform any one of the following functions:

1. As an 8-bit parallel port in mode-0 for input or output.

2. As two numbers of the 4-bit parallel port in mode-0 for input or output.

3. The individual pins of port-C can be set or reset for various control applications.

8255 Pin Diagram:

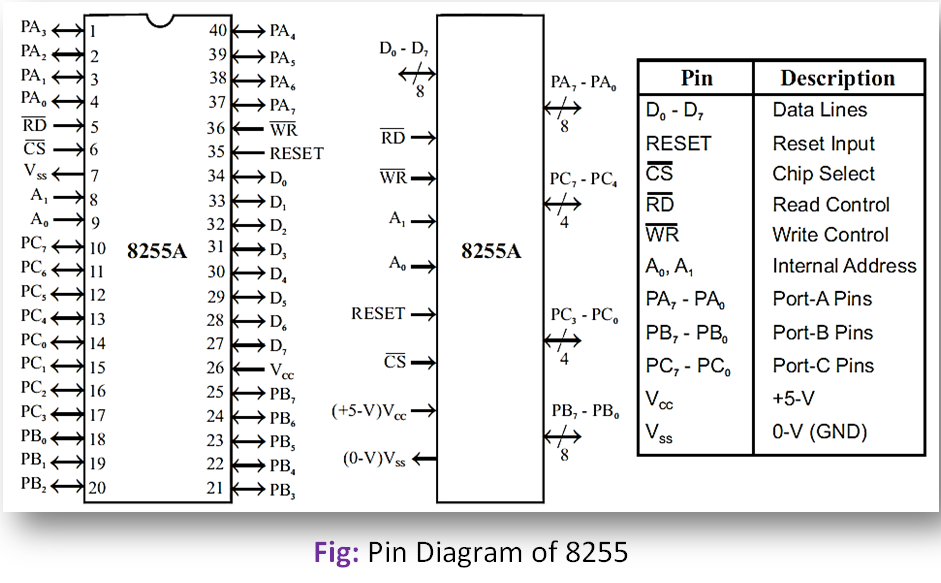

8255 has 40 pins and requires a single +5-V supply. The pin description of 8255 is shown in below Fig.

The ports are grouped as Group A and Group B. Group A has port-A, port-C upper, and its control circuit. Group B comprises port B, port C lower, and its control circuit. The read/write control logic requires six control signals. These signals are given below:

RD (Read): This control signal enables the read operation. When this signal is low, the microprocessor reads data from a selected IO port of the 8255A.

WR (Write): This control signal enables the write operation. When this signal goes low, the microprocessor writes into a selected IO port or the control register.

RESET: This is an active high signal. It clears the control register and set all ports in the input mode. CS, A0, and A1: These are device-select signals. The address lines A0 and A1 of 8255 can be connected to any two address lines of the processor to provide internal addresses.