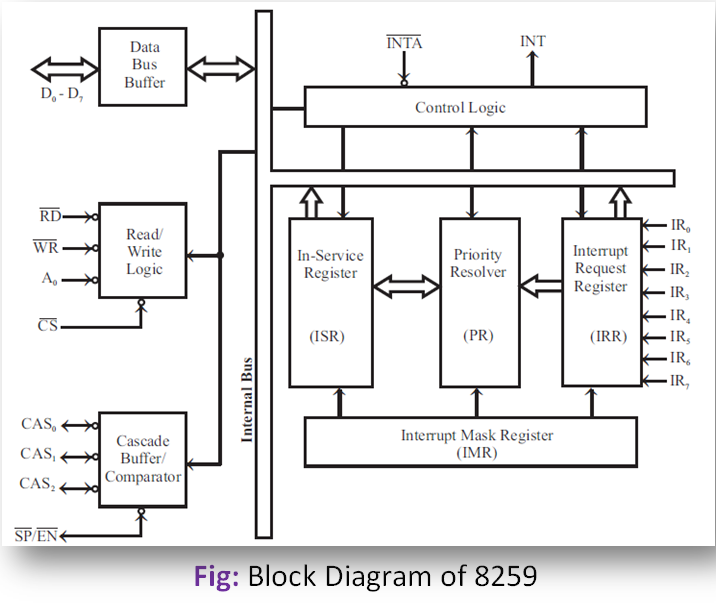

8259 Programmable Interrupt Controller:

The 8259 is a programmable interrupt controller. It is used to expand the interrupts of the 8085 or 8086 processors. One 8259 can accept eight interrupt requests and allows one by one to the processor INTR pin. The interrupt controller can be used in cascaded mode to expand the interrupts up to 64.

Features of 8259:

1. It is programmed to work with either an 8085 or 8086 processor.

2. It manages 8 interrupts according to the instructions written into its control registers.

3. The 8086 processor-based system, supplies the type number of the interrupt and the type number is programmable. In the 8085 processor-based system, it vectors an interrupt request anywhere in the memory map, and the interrupt

vector address is programmable.

4. The priorities of the interrupts are programmable. The different operating modes which decide the priorities are

automatic rotation mode, specific rotation mode, and fully nested mode.

5. Interrupts can be masked or unmasked individually.

6. The 8259 is programmed to accept either a level-triggered interrupt signal or an edge-triggered interrupt signal.

7. The 8259 provides the status of pending interrupts, masked interrupts, and interrupts being serviced.

8. The 8259s can be cascaded to accept a maximum of 64 interrupts.